최근 반도체 소형화와 반도체 성능을 향상시키기 위해 반도체 칩을 3D 적층하는 기술인 이종직접기술이 요구되고 있습니다.

이종직접기술은 칩의 수평 배열이 아닌 수직 배열 적층을 함으로써 면적을 최소화하고 반도체 성능을 향상시킬 수 있습니다.

3D 적층 기술이 개발되면서 전기적 연결 통로는 만드는 본딩 공정 기술도 함께 발전했습니다.

오늘은 반도체 후공정 본딩 기술 발전 방향(와이어 본딩, 플립칩 본딩, TSV, 하이브리드 본딩)에 대해서 알아보겠습니다.

본딩(Bonding)이란

본딩(Bonding)은 반도체 칩과 기판을 접착하는 것을 의미하며, 칩과 외부와의 전기적 연결 신호를 만들어주는 과정입니다.

패키징 공정의 일부인 본딩이 잘못되면 전공정에서 만들어진 반도체 칩은 전기적 작동을 전혀 할 수 없습니다.

본딩 기술의 발전

반도체 본딩 기술은 초기 금속와이어를 사용하는 와이어 본딩 방식을 사용했습니다.

하지만 반도체 성능 향상 및 반도체 패키지 소형화가 어려운 단점이 있어 이를 개선하기 위해 플립칩 본딩, TSV(Through Silicon Via), 하이브리드 본딩(Hybrid Bonding, Bump-less) 기술로 발전됐습니다.

| 와이어 본딩 | 플립 칩 본딩 | TSV | 하이브리드 본딩 | |

| 메모리 어플리케이션 | D램(모바일), 낸드 | D램 (컴퓨팅, 그래픽) | D램 (HPC/서버, 그래픽) | D램 (HPC/서버, 그래픽) |

| I/O 수 | ×4, ×8, ×16 | ×4, ×8, ×16 | ×1024 | ×1024 |

| 물리적 인터커넥션 수 | 50~150 | 150~200 | 3500~10000 | 3500~10000 |

| 인터커넥션 길이 | 200~2000um | 50um | 20um | 5um |

| 스택 수 | 2/4/6/8 | 1/2 | 4/8/12 | 4/8/12/16 |

| 최대용량/패키지 | 16GB | 4GB | 24GB | 32GB |

(1) 와이어 본딩

1965년에 금속와이어를 활용하는 사용하는 와이어 본딩(Wire Bonding) 기술은 1965년 금속와이어를 사용하는 방법으로 개발되어 현재도 사용되고 있습니다.

하지만 칩과 기판을 연결하는 금속배선의 길이가 길어 전기적 특성이 좋지 않고, 많은 공간을 차지하여 패키지 소형화가 어려운 단점이 있습니다.

(2) 플립칩 본딩(Flip-Chip Bonding)

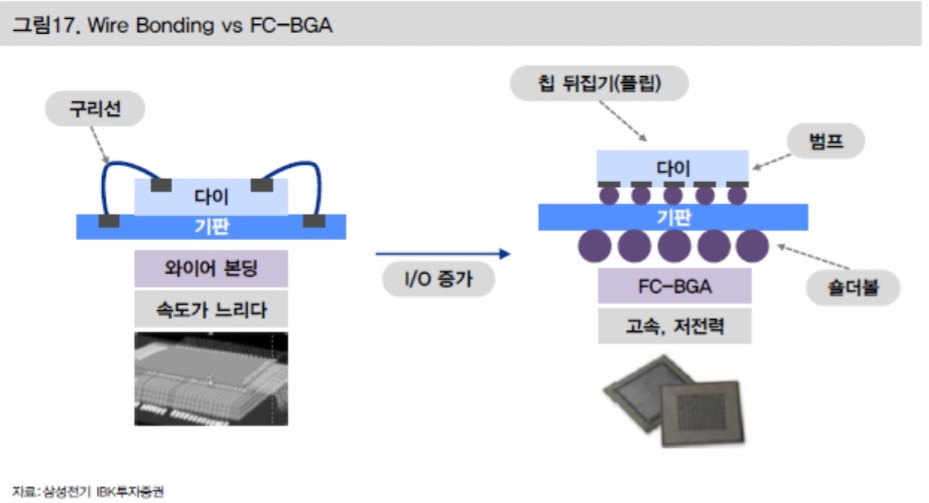

플립칩 본딩(Flip-Chip Bonding)은 기존에 사용하던 금속배선(와이어) 대신 범프라는 금속 물질을 사용하여 전기적 연결 통로를 만드는 방법입니다.

플립칩 본딩은 칩의 본딩 패드에 범퍼를 바로 형성시켜 금속배선 대비 전자의 이동거리가 짧아져 전기적 효율성이 좋아집니다.

뿐만 아니라 범프 크기가 작아 더 많은 범프를 접합시킬 수 있어 I/O단자의 개수를 증가시킬 수 있습니다.

I/O단자 증가로 한 번에 더 많은 데이터를 전송할 수 있는 장점이 있습니다.

(3) TSV(Through Silicon Via)

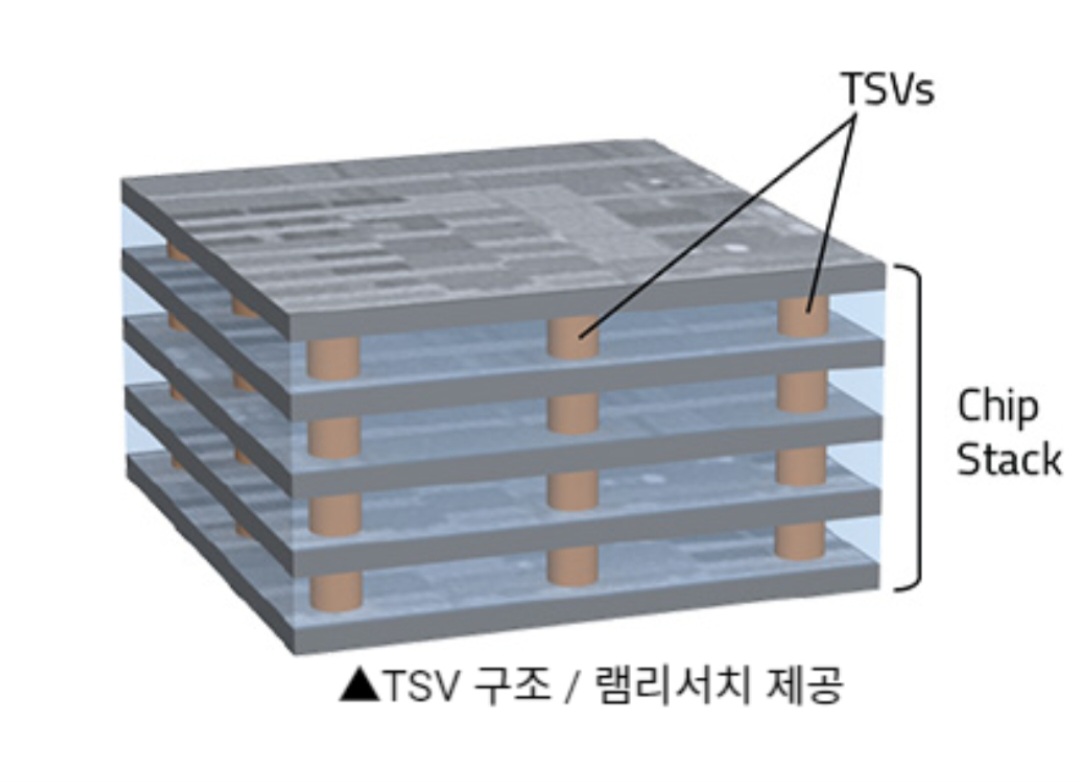

TSV(Through Silicon Via)는 3D 적층 기술에 요구되는 기술입니다.

TSV는 칩에 미세한 구멍(Via)을 뚫어, 칩과 칩 또는 칩과 기판을 연결 가능하므로 전자의 이동거리가 짧아 전기적 효율성이 좋고 패키지 소형화가 가능합니다.

(4) 하이브리드 본딩(Hybrid Bonding, Bump-less)

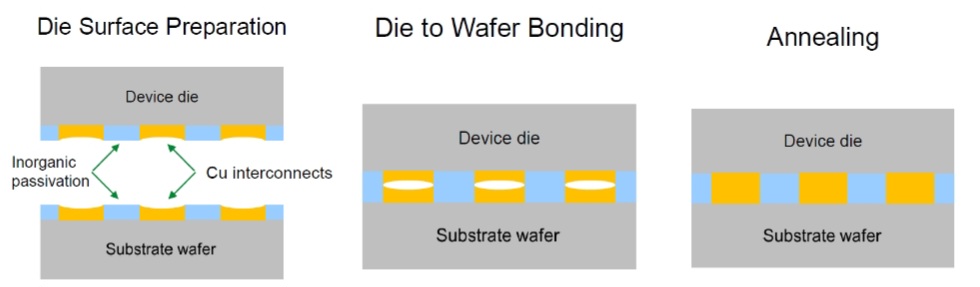

최근에 사용하는 마이크로범프(범프의 직경이 10-100㎛)가 작아지며 직경을 10-20㎛ 이하로 줄이는데 어려움이 있습니다.

마이크로범프(범프의 직경이 10-100㎛)의 기술 한계를 극복하기 위해 범프를 사용하지 않고 적층하려는 반도체 칩에 구리패드를 형성한 후 각 칩의 구리패드를 직집 연결하여 전기적 연결통로는 만드는 방식입니다.

지금까지 반도체 후공정 본딩 기술 발전 방향(와이어 본딩, 플립칩 본딩, TSV, 하이브리드 본딩)에 대해서 알아보았습니다.

함께 읽으면 좋은 글

(관심 종목) 고성능 기판(칩렛, 고다층화, 대면적화) 수혜주 기가비스

자율주행(영상 인식)과 챗봇(언어 모델)의 혁신으로 인해 AI 반도체의 수요가 급증하고 있습니다. AI 반도체의 발전과 함께 고사양 패키징 공정과 패키지 기판 기술에도 큰 변화가 나타나고 있습

chd0803.tistory.com

어드밴스드 패키징의 모든 것

현재의 반도체 업황은 응용처 뿐 아니라, 제품에 따라서 완전히 차별화 되는 국면이 나오고 있다. 현재 메모리에서 가장 주목해야할 부분은 "High-End DRAM". 삼성전자와 SK하이닉스 2Q 컨콜에서 "DDR5"

chd0803.tistory.com

반도체 후공정 패키지 기술의 이해(SoC, SiP, FOWLP, PLP)

우리나라 대표 산업으로 자리매김하고 있는 반도체 산업에 대해서 알아보자. 특히 웨이퍼 단위에서 이어지는 전공정과 칩이 완료된 후에 이뤄지는 후공정 패키지 분야에 대해서 알아보자. 반도

chd0803.tistory.com

'경제를 배우자.' 카테고리의 다른 글

| 24년 HBM 시장 규모가 증권가 예상의 4배 증가 (0) | 2024.02.24 |

|---|---|

| (투자 아이디어) 차량용 반도체 시장의 변화 (수혜주 - 텔레칩스, 넥스트칩, FC-BGA, 삼성전자) (1) | 2024.02.24 |

| SK하이닉스 HBM3E 세계 최초 양산 (SK하이닉스 & HBM 관련주) (1) | 2024.02.23 |

| 수은법 개정안 국회 소위 통과, K-방산 수혜주(현대로템, LIG넥스원, 한화에어로스페이스, 아이쓰리시스템) (0) | 2024.02.23 |

| (투자 아이디어) NEW 정책주! 스마트팜 & 그린벨트 해제 관련주(그린플러스, 우듬지팜) (0) | 2024.02.22 |

댓글